En diciembre,Wikichip informóque el proceso de 3 nm de TSMC prácticamente no mostró ninguna mejora en la densidad con respecto al nodo de 5 nm anterior de la compañía con respecto a la densidad de SRAM. La publicación planteó una pregunta simple: ¿Acabamos de presenciar la muerte de SRAM? Al menos en la opinión de Wikichip, "el escalamiento histórico está oficialmente muerto".

Esta idea tiene ramificaciones enormes para toda la industria tecnológica y sus efectos se sentirán en los PC y otros dispositivos durante años. Pero quizás te estés preguntando qué significa todo esto y si debería importarte. Para entender cómo afectará la "muerte de la SRAM" a los PC y cómo la afrontarán los diseñadores de chips, tenemos que hablar de los nodos, la Ley de Moore y la memoria caché.

La Ley de Moore estaba muriendo gradualmente, y ahora de repente

La Ley de Moore es el parámetro de éxito de la industria de semiconductores y sostiene que los chips más nuevos deben tener el doble de transistores que los chips de hace dos años. Intel, AMD y otros diseñadores de chips quieren asegurarse de que están a la altura de la Ley de Moore, y no hacerlo significa perder la ventaja tecnológica frente a los competidores.

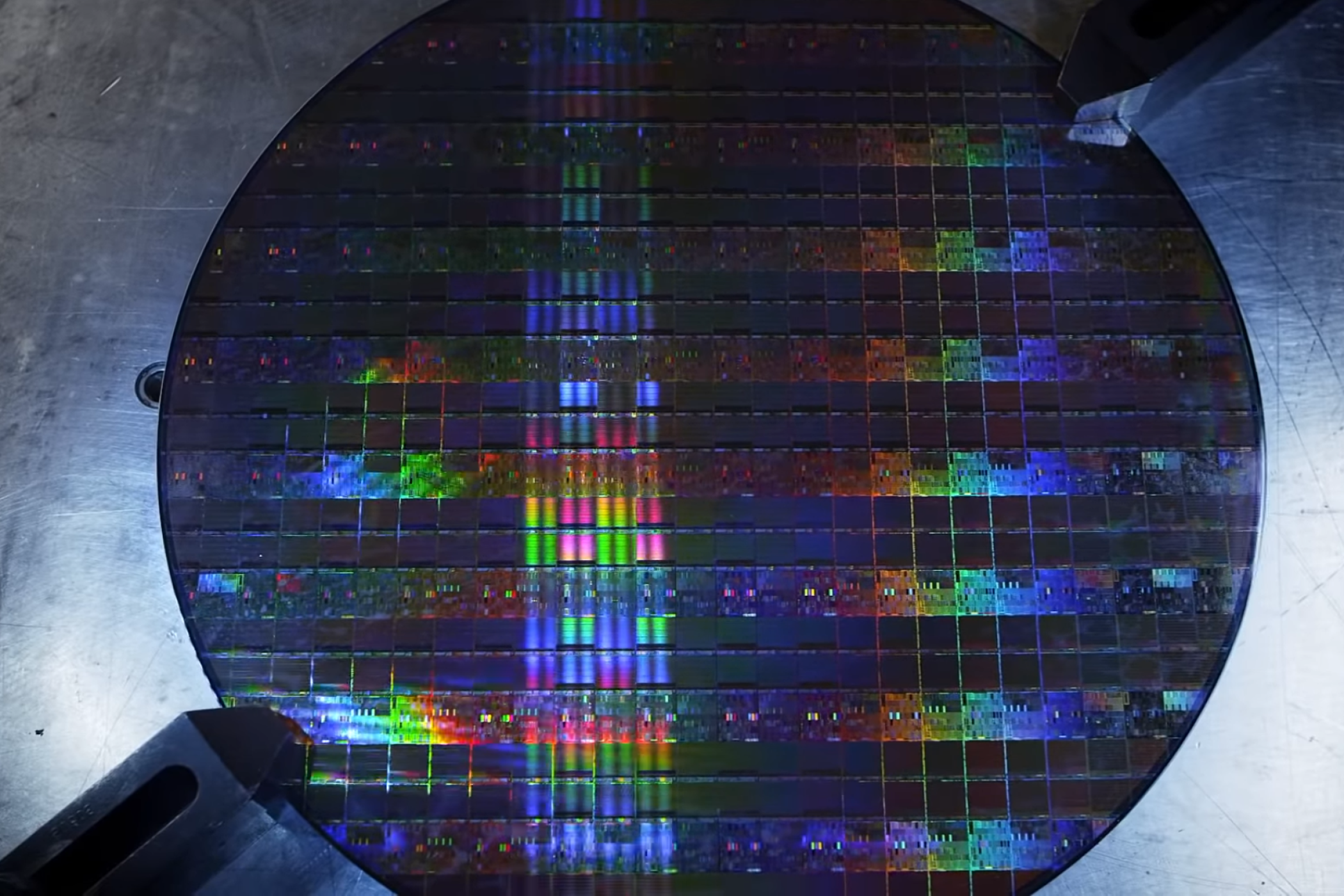

Como los procesadores solo pueden tener un tamaño determinado, la única forma fiable de aumentar la cantidad de transistores es reducir su tamaño y agruparlos de forma más densa. Un nodo o proceso es la forma en que un fabricante de semiconductores (también llamado fábricas y fundiciones) fabrica un chip; un nodo suele definirse por el tamaño de un transistor, por lo que cuanto más pequeño, mejor. Actualizarse al último proceso de fabricación siempre fue una forma fiable de aumentar la cantidad de transistores y el rendimiento, y durante décadas, la industria ha podido cumplir con todas las expectativas.

Lamentablemente, la Ley de Moore lleva años muriendo, desde aproximadamente 2010, cuando la industria alcanzó la marca de los 32 nm. Cuando intentó ir más allá, se topó con un muro de piedra. Casi todas las fábricas, desde TSMC hasta Samsung y GlobalFoundries, tuvieron dificultades para desarrollar algo más pequeño que 32 nm. Con el tiempo, se desarrollaron nuevas tecnologías que hicieron posible el progreso una vez más, pero los transistores ya no se hacen más pequeños de la misma manera que antes. El nombre de un nodo ya no refleja lo pequeño que es realmente el transistor, y los nuevos procesos ya no aportan las ganancias de densidad que solían aportar.

La industria se topó con un muro cuando intentó ir más allá de la marca de 32 nm en 2010.

¿Qué ocurre entonces con el nodo de 3 nm de TSMC? Bueno, hay dos tipos principales de transistores que se encuentran en un procesador típico: los de lógica y los de SRAM, o caché. La lógica ha sido más fácil de reducir que la caché durante un tiempo (la caché ya es muy densa), pero esta es la primera vez que hemos visto que una fundición como TSMC no logra reducirla en absoluto en un nuevo nodo. Se espera una variante de 3 nm con una densidad de caché significativamente mayor en algún momento, pero TSMC ciertamente llegó a un punto de inflexión en el que el escalamiento es muy menor y otras fábricas pueden encontrarse con el mismo problema.

Pero el problema no es sólo la imposibilidad de aumentar la cantidad de caché sin utilizar más área. Los procesadores sólo pueden ser tan grandes, y cualquier espacio que ocupe la caché es espacio que no se puede utilizar para la lógica, o para los transistores que conducen a mejoras directas de rendimiento. Al mismo tiempo, los procesadores con más núcleos y otras características necesitan más caché para evitar cuellos de botella relacionados con la memoria. Aunque la densidad de la lógica sigue aumentando con cada nuevo nodo, puede que no sea suficiente para compensar la falta de escalabilidad de la SRAM. Este podría ser el golpe de gracia para la Ley de Moore.

Cómo la industria puede resolver el problema de la SRAM

Los procesadores de alto rendimiento deben cumplir tres objetivos: el tamaño es limitado, se requiere caché y los nuevos nodos ya no reducirán mucho el tamaño de la caché, si es que lo hacen. Si bien es posible aumentar el rendimiento mediante mejoras arquitectónicas y velocidades de reloj más altas, agregar más transistores siempre ha sido la forma más fácil y consistente de lograr un aumento de velocidad generacional. Para superar este desafío, uno de estos aspectos fundamentales debe cambiar.

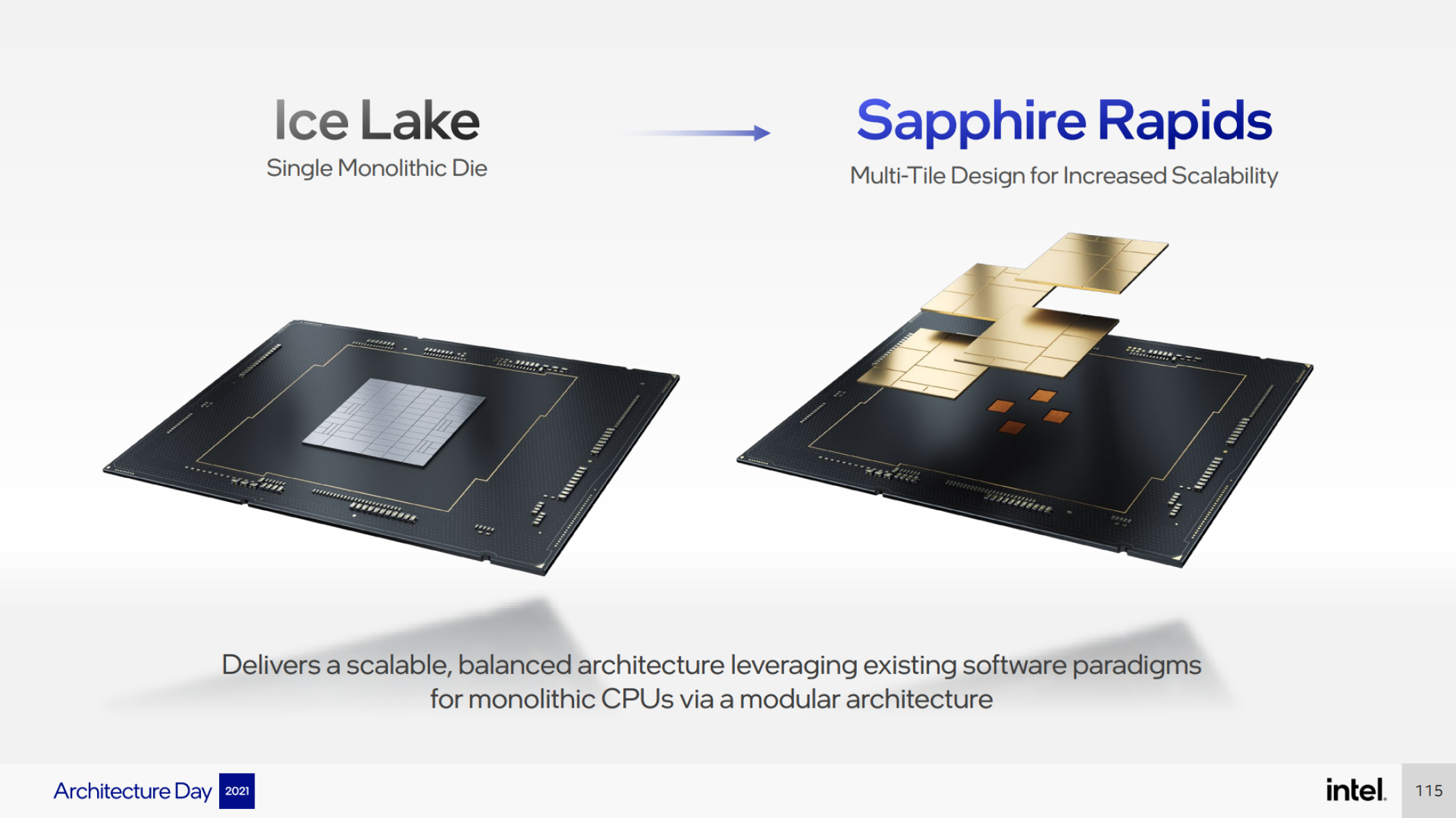

Resulta que ya existe una solución que funciona perfectamente para el problema de la memoria SRAM: los chiplets. Es la tecnología que AMD ha estado utilizando desde 2019 para sus CPU de escritorio y servidores. Un diseño de chiplet utiliza múltiples piezas de silicio (o matrices), y cada matriz tiene una o solo unas pocas funciones; algunas pueden tener solo núcleos, por ejemplo. Esto se opone a un diseño monolítico donde todo está en una sola matriz.

Los chiplets resuelven el problema del tamaño y son una parte clave de por qué AMD ha podido cumplir con la Ley de Moore. Recuerde, la Ley de Moore no se trata dedensidad, sinode número de transistores. Con la tecnología de chiplets, AMD ha podido crear procesadores con un área total de chip de más de 1000 mm2; fabricar esta CPU en un solo chip es probablemente imposible.

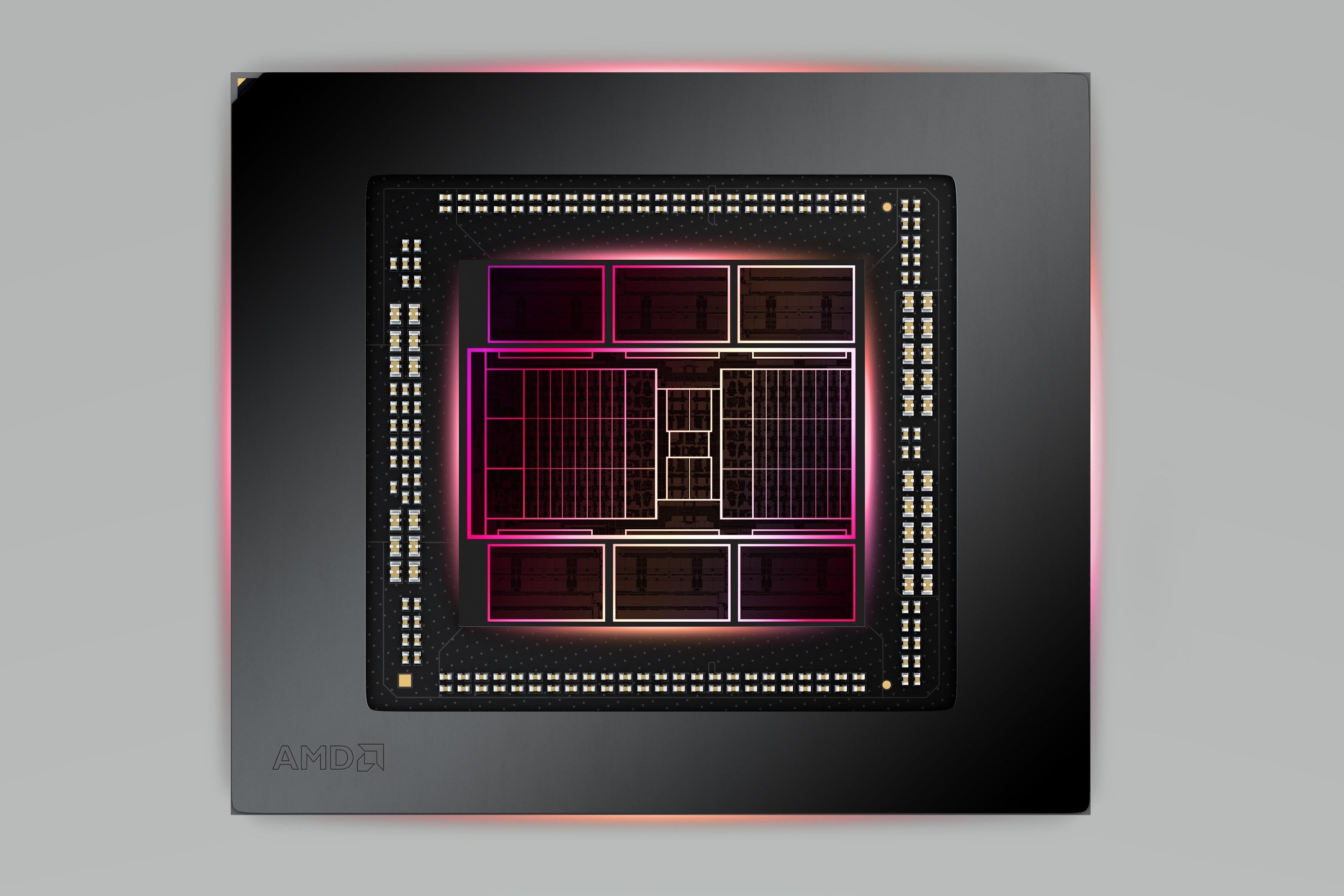

La medida más importante que ha tomado AMD para mitigar el problema de la caché es colocar la memoria caché en su propio chip. El V-Cache dentro del Ryzen 7 5800X3D y los chiplets de memoria en laserie RX 7000son un ejemplo de chiplets de caché en acción. Es probable que AMD haya visto lo que estaba por venir, ya que la caché ha sido difícil de reducir durante años y ahora que la caché se puede separar de todo lo demás, deja más espacio para chiplets más grandes con más núcleos. El chip principal de la RX 7900 XTX tiene solo unos 300 mm2, lo que significa que hay mucho espacio para que AMD haga un chip más grande si lo desea.

Pero los chiplets no son la única solución. El CEO de Nvidiaha proclamado recientemente la muerte de la Ley de Moore. La propia compañía se apoya en su tecnología de inteligencia artificial para conseguir un mayor rendimiento sin necesidad de alejarse de un diseño monolítico. Su nueva arquitectura Ada es teóricamente mucho más rápida que la Ampere de la última generación gracias a funciones como DLSS 3. Sin embargo, veremos en los próximos años si la Ley de Moore debe mantenerse viva o si las nuevas tecnologías pueden reflejar los beneficios de rendimiento que supone añadir más transistores sin tener que añadir ninguno.