En el mundo en constante crecimiento de la inteligencia artificial, las unidades de procesamiento neuronal (NPU) han surgido como un aspecto fundamental, lo que permite avances en el procesamiento y la tecnología de IA en dispositivos. Estos chips especializados están diseñados para manejar demandas computacionales intensas específicas de las redes neuronales, y ofrecen un rendimiento y una eficiencia que simplemente no pueden igualar las CPU convencionales de consumo. También son necesarias paraCopilot+, pero ¿qué son exactamente las NPU y cómo encajan en el panorama más amplio de la IA?

4 razones por las que no deberías desestimar las NPU y las PC con IA

Si bien ciertamente se utilizan como palabras de moda, las PC y NPU con IA tienen mucho que ofrecer.

La arquitectura de una NPU

Desglosando el diseño

En el corazón del diseño de una NPU se encuentra una arquitectura centrada en el paralelismo y la localización de los datos. A diferencia de las CPU y GPU de uso general, que están diseñadas para manejar una amplia gama de tareas (aunque las GPU también manejan una cantidad significativa en paralelo), las NPU están diseñadas específicamente para las demandas únicas de los cálculos de redes neuronales.

Con un enfoque en el paralelismo, las NPU cuentan con una gran variedad de núcleos de procesamiento. Estos núcleos son capaces de ejecutar múltiples instrucciones simultáneamente, lo que beneficia la naturaleza inherentemente paralela de las operaciones de las redes neuronales. Las redes neuronales a menudo implican la realización de la misma operación en diferentes puntos de datos simultáneamente, lo que tiene sentido ejecutar en paralelo. Además de eso, cada núcleo de una NPU puede manejar operaciones vectoriales y matriciales, que están en todas partes en los cálculos de redes neuronales. Al distribuir estas operaciones entre muchos núcleos, las NPU pueden lograr importantes ganancias de rendimiento.

Las NPU pueden emplear arquitecturas de instrucción única, múltiples datos (SIMD) o de instrucción múltiple, múltiples datos (MIMD). La SIMD permite aplicar una única instrucción a múltiples puntos de datos simultáneamente, mientras que la MIMD permite que diferentes núcleos ejecuten diferentes instrucciones simultáneamente. Esto brinda flexibilidad para optimizar las operaciones en las capas de la red neuronal.

Además del paralelismo, las NPU incorporan jerarquías de memoria especializadas. Estas jerarquías están diseñadas para garantizar que los datos estén lo más cerca posible de las unidades de procesamiento, reduciendo así el tiempo y la energía necesarios para obtener los datos. Esto puede significar que hay SRAM en el chip, que es una memoria más rápida y de baja latencia para almacenar datos intermedios, pesos y activaciones durante el procesamiento de la red neuronal. Esto tiene ventajas, ya que mantener los datos a los que se accede con frecuencia en el chip significa que las NPU minimizan la necesidad de acceder a DRAM más lenta fuera del chip, lo que reduce significativamente la latencia y el consumo de energía.

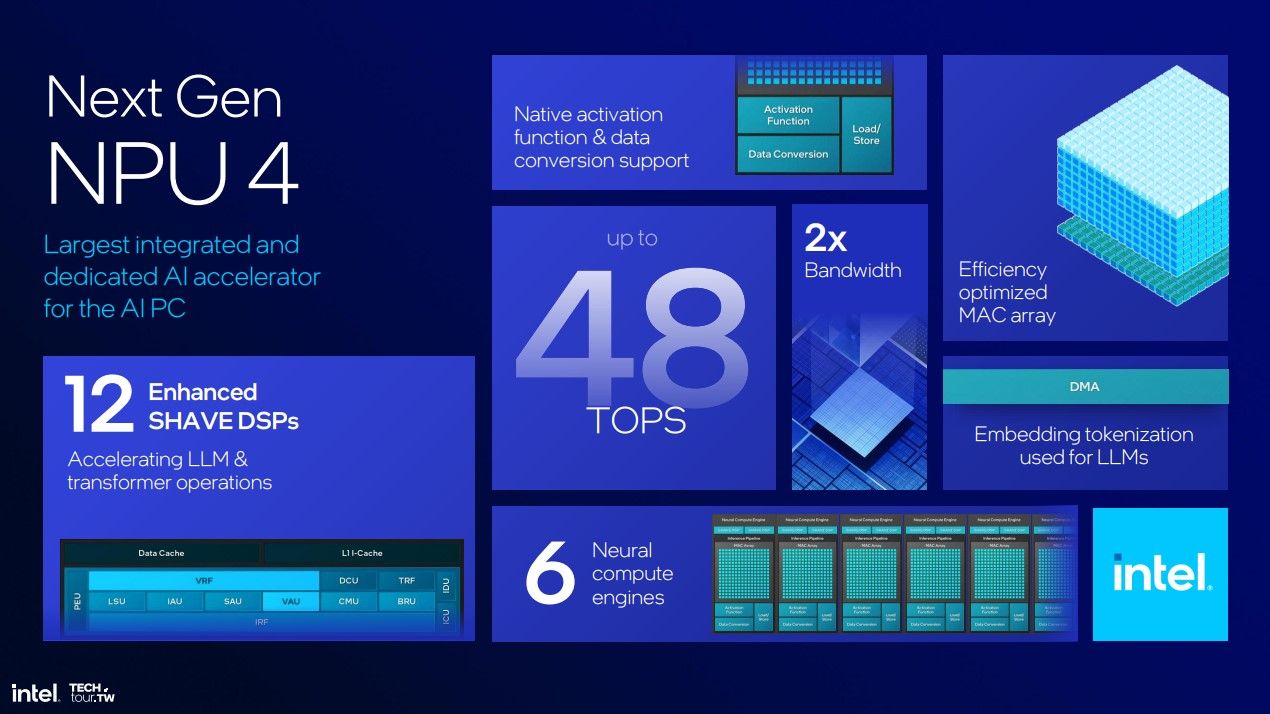

Además, las NPU también pueden contar con sistemas de caché de varios niveles, con cachés L1 y L2 que brindan capas adicionales de memoria de acceso rápido. Estas cachés almacenan datos e instrucciones a los que se accedió recientemente, lo que mejora aún más la localización de los datos y reduce los tiempos de acceso. Los motores de cómputo neuronal Meteor Lake de Intel (como los núcleos de una NPU) no tienen una caché L1 o L2, pero sí tienen acceso a 2 MB de SRAM por NCE.

En lo que respecta a la computación, las unidades de procesamiento tensorial (TPU) dedicadas, que están diseñadas específicamente para manejar las operaciones matemáticas fundamentales para las redes neuronales, manejan la mayor parte de la carga de trabajo. Las redes neuronales dependen en gran medida de multiplicaciones de matrices y operaciones de convolución, y las TPU dentro de las NPU están optimizadas para estas operaciones, con aceleradores de hardware que pueden realizar grandes multiplicaciones de matrices y convoluciones. Estos aceleradores hacen uso del paralelismo de datos al ejecutar operaciones en múltiples puntos de datos simultáneamente.

Las NPU pueden procesar varias capas de una red neuronal a la vez, desde capas densas completamente conectadas hasta capas convolucionales. El paralelismo permite que las NPU procesen grandes cantidades de datos, acelerando tanto las fases de entrenamiento como de inferencia. Muchas NPU utilizan matrices sistólicas, una arquitectura de computación paralela diseñada para manejar los patrones de flujo de datos repetitivos y regulares de las operaciones de redes neuronales. Las matrices sistólicas consisten en una cuadrícula de elementos de procesamiento (PE) que pasan datos a través de la matriz, lo que permite cálculos de alto rendimiento y baja latencia y acelera las multiplicaciones de matrices.

Por último, las NPU suelen incluir controladores de acceso directo a memoria (DMA) que permiten transferir datos entre la memoria y las unidades de procesamiento sin necesidad de que los núcleos computacionales hagan nada. Esto permite que los núcleos se concentren en el cálculo, lo que a su vez mejora el rendimiento general.

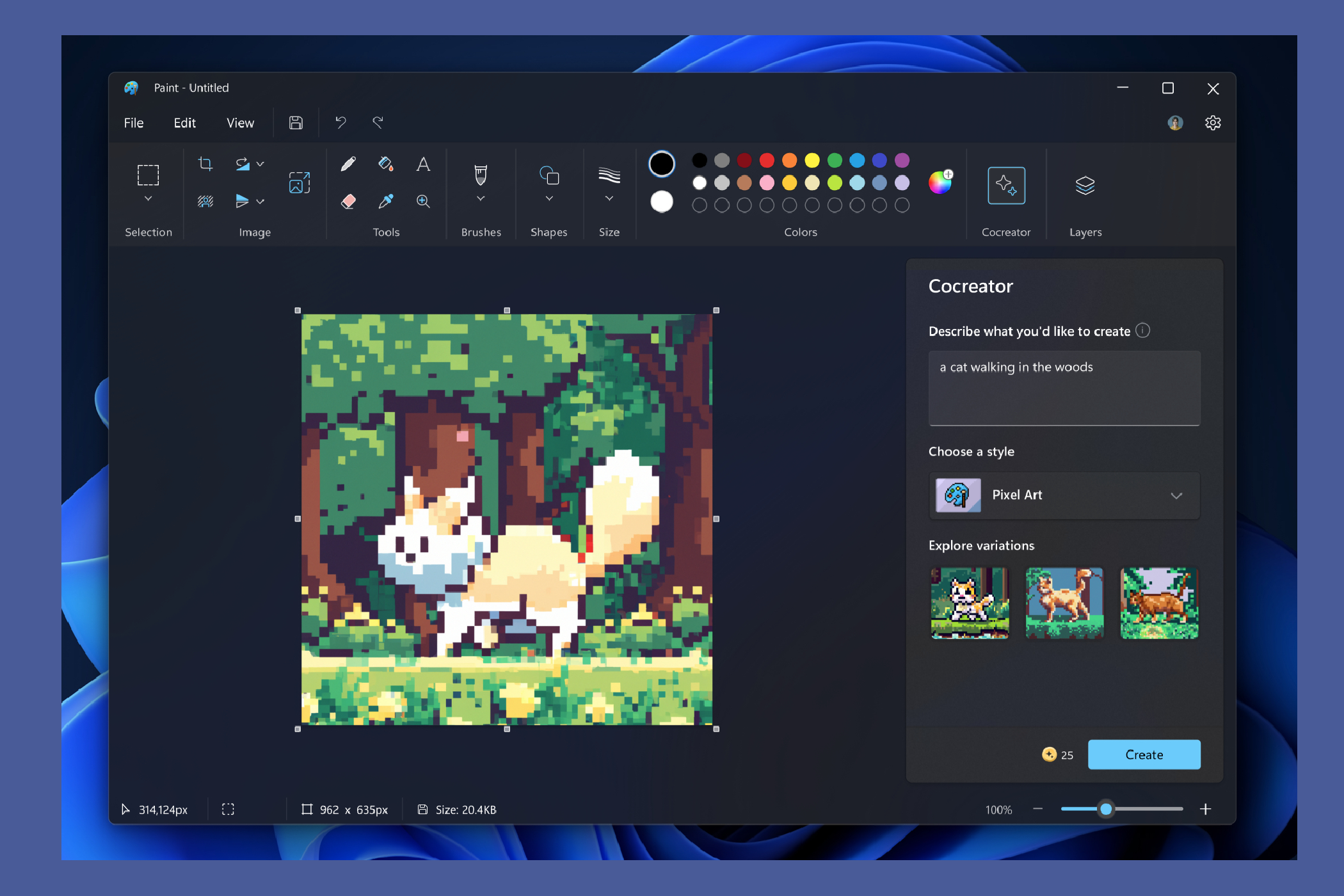

3 cosas que me gustaría ver en la nueva aplicación Paint NPU de Microsoft

Paint NPU está en camino, pero aún no estamos seguros de qué hará.

Una NPU será cada vez más importante

Al menos para la IA en el dispositivo

Tu próxima computadora portátil probablemente tendrá una NPU, al menos si está equipada con un chipInteloRyzenreciente . Qualcomm también tiene su propia NPU, y el motor neuronal de Apple también es una NPU. Son cada vez más importantes para administrar las cargas de trabajo de IA en el dispositivo de una manera más eficiente en términos de consumo de energía, aunque cada NPU es diferente. Tal como están las cosas, tenemos un montón de diferentes piezas de hardware NPU que los desarrolladores también buscan usar, y tienen diferentes capacidades.

Con el paso del tiempo, esperamos que las NPU se estandaricen un poco más, pero por ahora, la situación es un poco como en el lejano oeste. Hay muchos estándares nuevos y mucho hardware nuevo en prueba, por lo que la experiencia de cada uno es diferente.